# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale: MSTII - Mathématiques, Sciences et technologies de l'information, Informatique

Spécialité: Informatique Unité de recherche : VERIMAG

# Validation Formelle de Transformations Intra-Procédurales par **Simulation Symbolique Défensive**

# Formal Validation of Intra-Procedural Transformations by Defensive **Symbolic Simulation**

Présentée par :

# Léo GOURDIN

# Direction de thèse :

Sylvain BOULMÉ

Directeur de thèse

MAITRE DE CONFERENCES, Université Grenoble Alpes

Co-directeur de thèse Frédéric PÉTROT

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

# Rapporteurs:

Jean-Christophe FILLIÂTRE

DIRECTEUR DE RECHERCHE, CNRS Délégation Ile-de-France

Jens KNOOP

PROFESSEUR, Institute of Information Systems Engineering - TU Wien

# Thèse soutenue publiquement le 12 décembre 2023, devant le jury composé de :

Svlvain BOULMÉ Directeur de thèse

MAITRE DE CONFERENCES, Université Grenoble Alpes

**Delphine DEMANGE** Examinatrice

MAITRESSE DE CONFERENCES, Université de Rennes

Jean-Christophe FILLIÂTRE Rapporteur

DIRECTEUR DE RECHERCHE, CNRS Délégation Ile-de-France

Rapporteur

PROFESSEUR, Institute of Information Systems Engineering - TU Wien

Frédéric PÉTROT Co-directeur de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

**Marc POUZET** Examinateur

PROFESSEUR DES UNIVERSITES, École Normale Supérieure

**Gwen SALAÜN** Président

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

À René...

#### **FOREWORD**

#### HOW TO READ THIS DOCUMENT?

I recommend reading a digital, or at least colored, version of this document; but a printed version should be ok as well. Chapters, sections, or references marked with a dagger † present a personal contribution of my PhD work. The exhaustive list of my contributions is given in §1.3. Paragraphs, examples, or figures marked with an asterisk \* are partially or totally reused from another document (paper, article, draft) to illustrate a specific concept. Important notions are emphasized in *italic*, and very important ones in violet. Most folded acronyms used in the document are clickable links pointing to their definition.

The CompCert fork from Verimag, on which I worked during my PhD, is named Chamois-CompCert (see its brief description in §3.6). The whole Coq and OCaml code described in this document is available online in a frozen version of the Chamois-CompCert fork dedicated to this manuscript. See the git repository at <a href="https://framagit.org/yukit/compcert-chamois-gl-thesis">https://framagit.org/yukit/compcert-chamois-gl-thesis</a>. Some types, definitions, lemmas, or theorems are given in a mathematical notation rather than in Coq, mainly to simplify reading. Their actual implementation or documentation, when relevant to read, is linked with symbol [\$\displays \bigcirc (in the digital version).

Throughout this document, I use the term "mainline CompCert" to refer to the public version of CompCert (3.12) distributed by AbsInt, and available on GitHub at https://github.com/AbsInt/CompCert.

Since all the mathematical proofs presented throughout this document are formalized in the Coq proof assistant, with their code publicly available online (URL above), I will not detail every lemma or theorem, but I will rather give an *intuition* of proof decomposition.

#### **ABSTRACT**

Compilers are highly complex software systems and may, therefore, contain bugs. These bugs can result in errors during the compilation process, or, much more annoyingly, in the generation of incorrect code. Bugs that subtly alter the semantics of generated programs are often very insidious and challenging to trace. In certain applications, particularly in embedded, safety-critical systems subject to stringent regulations and requirements (e.g. avionics, trains, etc.), eliminating these bugs is of paramount importance.

Although most of these bugs are typically found in optimization passes, disabling optimizations is not a viable option in many applications. In fact, simply turning off optimizations is insufficient to guarantee bug-free code. Regulatory standards often necessitate the use of simple, predictable processors, heavily reliant on the compiler for performance.

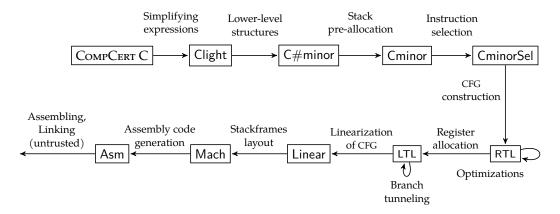

An alternative solution is to employ a certified compiler, mechanically proven correct in a proof assistant. Such a compiler ensures that the generated assembly code faithfully preserves the source code's semantics. CompCert belongs to this category, and stands as the first formally verified C compiler widely used in the industry. However, proving the correctness of intricate optimizations remains a challenge. This is why certified compilers, including CompCert, produce code that is significantly less performant compared to mainstream compilers like GCC or LLVM.

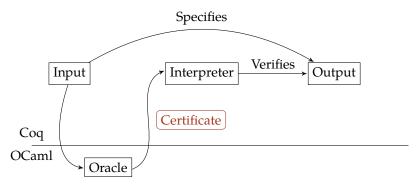

Translation validation offers a technique where only the result of an optimization is verified, rather than proving the correctness of its implementation. The optimization algorithm, referred to as an oracle, remains untrusted. Nevertheless, its results are always subjected to validation by a proven validator designed to reject any errors.

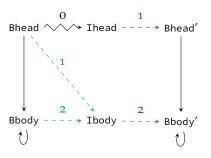

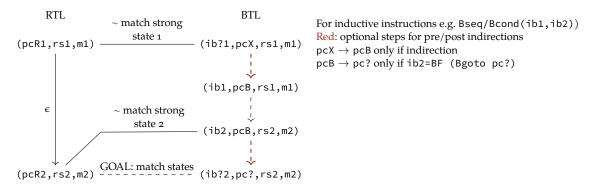

In this thesis, we delve into the concept of guided translation validation. The principle is to allow oracles to guide the validator by providing hints that reduce the search space, thereby minimizing the complexity of the validation process. Specifically, we propose a formally verified symbolic interpreter capable of validating an entire class of transformations. Our tool requests program invariants from oracles as hints to drive the symbolic simulation of both the original and optimized code. The proven simulation test defensively validates the applied optimizations, ensuring consistency with the unoptimized code.

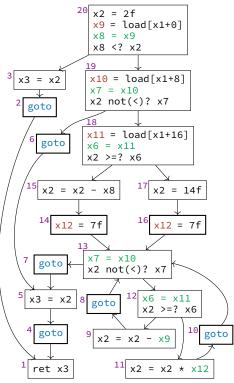

We have successfully validated several new transformations using this approach, including some that had never been formally verified before, thanks to the communication between oracles and their validator. Notably, we verify a strength-reduction optimization targeting 64-bit RISC-V architectures, which show promise in the context of safety-critical embedded systems. In addition to strength-reduction, our symbolic simulation framework also supports partial redundancy elimination, dead code elimination, code motion, scheduling, and weak software pipelining with renaming.

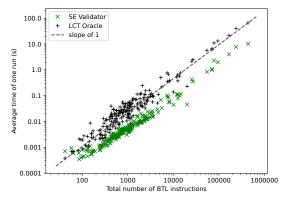

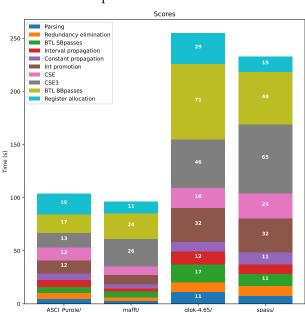

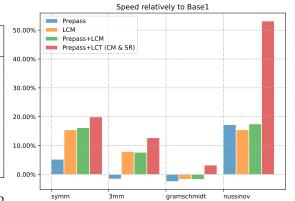

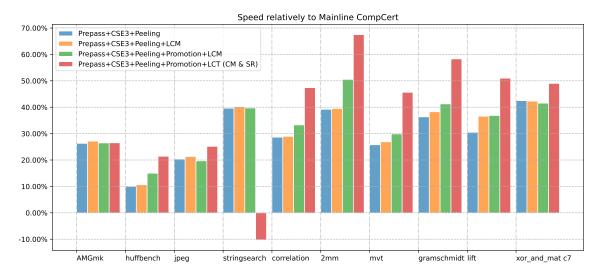

We have integrated our validation mechanism into a fork of CompCert through the development of a new intermediate language called Block Transfer Language, BTL. Translations to and from BTL are also defensively validated, accomplished with a separate, formally verified checker capable of validating code duplication and factorization as control-flow graph morphisms. To rigorously assess the impact of our optimizations and the overhead introduced by their validation, we conducted multiple experimental measurements of both compilation time and runtime performance. Platform specific optimizations were tested on both AArch64 and RISC-V architectures. Results show a significant improvement of the runtime performance while maintaining a reasonable compilation time.

In the future, this same method could potentially be applied to validate other transformations, such as the automatic insertion of security countermeasures. Our designs appear to be applicable beyond CompCert.

**Keywords:** Formal verification, Translation validation, Symbolic execution, Compiler optimizations, RISC-V, the Coq proof assistant, the CompCert compiler.

## RÉSUMÉ

Les compilateurs sont des systèmes logiciels très complexes et peuvent donc contenir des bogues. Ces bogues peuvent se traduire par des erreurs au cours du processus de compilation ou, plus ennuyeusement encore, par la génération d'un code incorrect. Les bogues qui altèrent subtilement la sémantique des programmes générés sont souvent très insidieux et difficiles à retracer. Dans certaines applications, en particulier dans les systèmes embarqués critiques pour la sécurité et sujets à des exigences et régulations strictes (par exemple, avionique, trains, etc.), l'élimination de ces bogues est d'une importance capitale.

Bien que la plupart de ces bogues soient typiquement situés dans les passes d'optimisation, la désactivation des optimisations n'est pas une solution viable dans de nombreuses applications. En fait, la simple désactivation des optimisations ne suffit pas à garantir un code exempt de bogues. Les normes réglementaires imposent en général l'utilisation de processeurs simples et prédictibles, dont la performance dépend largement du compilateur.

Une solution alternative est d'employer un compilateur certifié, mécaniquement prouvé correct dans un assistant de preuve. Un tel compilateur assure que le code assembleur généré préserve fidèlement la sémantique du code source. CompCert appartient à cette catégorie, et est le premier compilateur C formellement vérifié et largement utilisé dans l'industrie. Cependant, prouver la correction d'optimisations complexes reste un défi. C'est pourquoi les compilateurs certifiés, y compris CompCert, produisent un code significativement moins performant que les compilateurs classiques tels que GCC ou LLVM.

La validation de traduction est une technique où seul le résultat d'une optimisation est vérifié, plutôt que de prouver la correction de son implémentation. L'algorithme d'optimisation, appelé oracle, reste considéré comme non fiable. Néanmoins, ses résultats sont toujours soumis à la validation par un validateur prouvé et conçu pour rejeter toute erreur.

Dans cette thèse, nous approfondissons le concept de validation de traduction guidée. Le principe est de permettre aux oracles de guider le validateur en lui fournissant des indices qui réduisent l'espace de recherche, minimisant ainsi la complexité du processus de validation. Plus précisément, nous proposons un interpréteur symbolique formellement vérifié capable de valider toute une classe de transformations. Notre outil demande aux oracles des invariants de programme en tant qu'indices pour guider la simulation symbolique du code original et du code optimisé. Le test de simulation prouvé valide défensivement les optimisations appliquées, en garantissant leur cohérence vis-à-vis du code non optimisé.

Nous avons validé avec succès plusieurs nouvelles transformations en utilisant cette approche, dont certaines n'avaient jamais été formellement vérifiées jusqu'alors, grâce à la communication entre les oracles et leur validateur. Notamment, nous avons vérifié une optimisation de "strengthreduction" (littéralement, "réduction de force") ciblant les architectures RISC-V 64 bits, qui sont prometteuses dans le contexte des systèmes embarqués critiques pour la sécurité. En plus de la "strength-reduction", notre outil de simulation symbolique supporte l'élimination de redondances partielles, l'élimination du code mort, le déplacement de code, l'ordonnancement, et une forme faible de pipeline logiciel avec renommage.

Nous avons intégré notre mécanisme de validation dans notre version de développement (fork) de CompCert, en développant une nouvelle représentation intermédiaire nommée "Block Transfer Language", BTL (littéralement "Langage de Transfert en Blocs"). Les traductions de et vers BTL sont également validées de manière défensive, à l'aide d'un vérificateur dédié, formellement vérifié, et capable de valider de la duplication et factorisation de code en tant que morphismes des graphes de flux de contrôle. Pour évaluer rigoureusement l'impact de nos optimisations et le temps de compilation supplémentaire induit par leur validation, nous avons effectué de multiples mesures expérimentales du temps de compilation et des performances à l'exécution. Les optimisations spécifiques à une architecture cible ont été testées sur des plateformes AArch64 et RISC-V. Les résultats montrent une amélioration significative des performances à l'exécution tout en maintenant un temps de compilation raisonnable.

À l'avenir, cette même méthode pourrait potentiellement être appliquée pour valider d'autres transformations, comme l'insertion automatique de contre-mesures de sécurité. Nos conceptions semblent être applicables au-delà de CompCert.

Mots clefs : Vérification formelle, Validation de traduction, Exécution symbolique, Optimisations de compilateur, RISC-V, l'assistant de preuve Coq, le compilateur certifié СомРСЕRТ.

#### ACKNOWLEDGMENTS

I'd like to start by expressing my deepest thanks to Sylvain. Thank you for all the help you gave me in designing and completing this thesis, for your advice, the time you spent discussing and reflecting with me, the many ideas and comments you contributed, and without which I wouldn't have been able to complete this work. Thank you for believing in me and listening to me during these three years. Thank you for everything. I'd also like to extend the same profound thanks to Frédéric; it hasn't always been easy to find the time to work together at TIMA, but you've always been available and willing to listen, to help, and support me. I'm truly grateful. My sincere thanks also to David. Although you were not officially my thesis supervisor, you've been a great help to me during these three years, with your many ideas, your enthusiasm, and your patience in the rigorous proofreading of this manuscript. I'll never have enough words to express how grateful I am to all three of you.

I'd like to thank all the members of my thesis jury. Thank you, Jean-Christophe Filliâtre and Jens Knoop for agreeing to read, review, and report on this manuscript, and for providing helpful and thoughtful feedback. It's a great honor. Most notably, Jean-Christophe Filliâtre, thank you for your extensive notes on the manuscript; Jens Knoop, thank you for the very interesting scientific discussion we had before the reports. Thank you also to Marc Pouzet and Gwen Salaün for accepting to be part of my thesis jury and for your interest in my thesis. Thank you, Delphine Demange, not only for being part of this jury but also for agreeing to follow my thesis as an external expert over the past three years. Our exchanges were important and meaningful for me, and your outside view helped me to have confidence in my work.

I also thank all my colleagues in the Verimag laboratory, who have given me the chance to work in a pleasant and caring environment. I'd especially like to thank Karine for following my progress over the last six years, and for listening to me and advising me on my decision to do a thesis three years ago. I'm also incredibly grateful to Olivier, with whom it's always been a pleasure to work. Thank you for your constant good mood, the moments spent laughing, and our endless discussions. You're the person I knew I needed to talk to to cheer me up! I'm thankful as well to Marie-Laure, who allows me to continue my research at Verimag and to meet the security research community.

I'd also like to extend my warmest thanks to all my friends from the academic world, for all our moments spent together, our coffee breaks, our discussions, our odd days at Eve, and for your essential good humor. Aina, Alban, Alexandre H. from Inria, and Alexandre B. from Verimag, Ana, Baptiste, Basile my new office colleague, Cyril, Hadi, Lucas, Marco, Doctor Thomas M., not-yet-doctor Thomas V. Thank you for being there. I'm really happy to have been able to meet such good friends during this thesis, and I wish you the best. Thank you also to Abderrahmane, Benjamin, Etienne, Oussama, and all the people I had good times with.

I'd like to give a huge thank you to my past roommates Léa and Olivier, and to my present roommates Adrien, Tom, and Vincent. And Solenne, who is almost a roommate too. Thank you for putting up with my changing moods, and thank you for your support, which really meant a lot to me during these three years.

I'd like to send a special thank you to Soline. Thank you so much for being there; you're certainly one of the nicest people I've met, and my best friend.

I'd like to thank my family as well. Mom, Dad, Eric, thank you from the bottom of my heart for all your help and love. Thank you for supporting me, listening, and thank you for allowing me to spend these eight years at university peacefully. Christine, Stéphane, Lola, thank you for being there in Grenoble and always available to spend time together. More generally, thank you to my whole family for their unconditional love and kindness.

Last but not least, I'd like to send a special thank you to Leila. I can't even express how much you helped me. Thanks for everything, really.

#### REMERCIEMENTS

Je voudrais commencer par exprimer mes plus sincères remerciements à Sylvain. Merci pour toute l'aide que tu m'as apportée dans la conception et la réalisation de cette thèse, pour tes conseils, le temps que tu as consacré à discuter et à réfléchir avec moi, les nombreuses idées et commentaires que tu as apportés, et sans lesquels je n'aurais pas pu mener à bien ce travail. Merci d'avoir cru en moi et de m'avoir écouté pendant ces trois ans. Merci pour tout. J'aimerais également étendre ces remerciements sincères à Frédéric ; ce n'a pas toujours été facile de trouver le temps pour travailler ensemble à TIMA, mais tu as toujours été disponible et prêt à écouter, à aider, et à me soutenir. J'en suis vraiment reconnaissant. Mes remerciements les plus sincères également à David. Bien que tu n'aies pas été officiellement mon directeur de thèse, tu m'as énormément aidé au cours de ces trois ans, avec tes nombreuses idées, ton enthousiasme, et ta patience dans la relecture rigoureuse de ce manuscrit. Je n'aurai jamais assez de mots pour exprimer ma gratitude envers vous trois.

Je tiens à remercier tous les membres de mon jury de thèse. Merci, Jean-Christophe Filliâtre et Jens Knoop, d'avoir accepté de lire, de passer en revue, et de rapporter sur ce manuscrit, et pour vos commentaires utiles et réfléchis. C'est un grand honneur. Plus particulièrement, Jean-Christophe Filliâtre, merci pour vos nombreuses annotations sur le manuscrit ; Jens Knoop, merci pour la discussion scientifique très intéressante que nous avons eue avant les rapports. Merci aussi à Marc Pouzet et Gwen Salaün d'avoir accepté de faire partie de mon jury et pour votre intérêt pour ma thèse. Merci, Delphine Demange, non seulement de faire partie de ce jury, mais aussi d'avoir accepté de suivre ma thèse en tant qu'experte extérieure durant ces trois ans. Nos échanges ont été importants et significatifs pour moi, et ton regard extérieur m'a aidé à avoir confiance en mon travail.

Je remercie aussi tous mes collègues du laboratoire Verimag, qui m'ont donné l'opportunité de travailler dans un environnement agréable et bienveillant. J'aimerais particulièrement te remercier, Karine, pour avoir suivi ma progression au cours des six dernières années, et de m'avoir écouté et conseillé lorsque j'ai pris la décision de faire une thèse il y a trois ans. Je suis également incroyablement reconnaissant envers Olivier, avec qui il a toujours été un plaisir de travailler. Merci pour ta bonne humeur constante, les moments passés à rire, et nos discussions interminables. Tu es la personne avec qui je savais qu'il fallait parler pour me remonter le moral! Je suis également reconnaissant envers Marie-Laure, qui me permet de poursuivre ma recherche à Verimag et de rencontrer la communauté de recherche en sécurité.

J'aimerais également étendre mes remerciements les plus chaleureux à tous mes amis du monde académique, pour tous nos moments passés ensemble, nos pauses café, nos discussions, nos jours impairs à Eve, et pour votre bonne humeur essentielle. Aina, Alban, Alexandre H. de l'Inria, et Alexandre B. de Verimag, Ana, Baptiste, Basile, mon nouveau collègue de bureau, Cyril, Hadi, Lucas, Marco, docteur Thomas M., futur docteur Thomas V. Merci d'être là. Je suis vraiment heureux d'avoir pu rencontrer de si bons amis au cours de cette thèse, et je vous souhaite tout le meilleur. Merci également à Abderrahmane, Benjamin, Etienne, Oussama, et à toutes les personnes avec lesquelles j'ai passé de bons moments.

J'aimerais donner un immense merci à mes anciens colocataires, Léa et Olivier, et à mes colocataires actuels, Adrien, Tom, et Vincent. Et Solenne, qui est presque une colocataire aussi. Merci de supporter mes humeurs changeantes, et merci pour votre soutien, qui a signifié vraiment beaucoup pour moi au cours de ces trois ans.

J'aimerais envoyer un remerciement spécial à Soline. Merci beaucoup d'être là ; tu es certainement l'une des personnes les plus gentilles que j'ai rencontrées, et ma meilleure amie.

J'aimerais également remercier ma famille. Maman, Papa, Éric, merci du fond du cœur pour toute votre aide et votre amour. Merci de me soutenir, de m'écouter, et merci de m'avoir permis de passer ces huit ans à l'université en toute tranquillité. Christine, Stéphane, Lola, merci d'être là à Grenoble et toujours disponibles pour passer du temps ensemble. Plus généralement, merci à toute ma famille pour son amour inconditionnel et sa gentillesse.

Enfin, mais non le moindre, j'aimerais envoyer un remerciement spécial à Leila. Je ne peux même pas exprimer à quel point tu m'as aidé. Merci pour tout, vraiment.

# CONTENTS

| 1 | Intro | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1          |

|---|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1 | 1.1   | Certified Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1          |

|   | 1.1   | 1.1.1 Security and Safety of Programs and Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1          |

|   |       | 1.1.2 Safety-Critical Systems (SCS) & Compilers Bugs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          |

|   |       | 1.1.2 Main Types of Intermediate Representations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3          |

|   | 1.2   | Purpose of This Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>4     |

|   | 1.2   | 1.2.1 Motivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4          |

|   |       | 1.2.2 A Simplified Example of Global Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

|   | 1.3   | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7          |

|   | 1.5   | 1.3.1 Exhaustive List With Links to Relevant Sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7          |

|   |       | 1.3.2 Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8          |

|   | 1.4   | Contents of This Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9          |

|   |       | Constitution of the decimal of the constitution of the constitutio | 7          |

| I | Setti | ing & Preliminary Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 2 | Forr  | mally Verified Defensive Programming (FVDP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11         |

|   | 2.1   | The Coq Proof Assistant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11         |

|   | 2.2   | Translation Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11         |

|   |       | 2.2.1 A Classical Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11         |

|   |       | 2.2.2 Using "Shadow" Fields to Combine Extracted and Handwritten OCaml Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12         |

|   |       | 2.2.3 Symbolic Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12         |

|   | 2.3   | The Principle of Defensive Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14         |

|   | 2.4   | Impure: A Safe Foreign Function Interface (FFI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15         |

|   |       | 2.4.1 The Risk of "Impurity"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15         |

|   |       | 2.4.2 Motivation: FVDP of a Lightweight Hash-Consing Factory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16         |

|   |       | 2.4.3 A Coq Model of OCaml Pointer Equality?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16         |

|   |       | 2.4.4 The May-Return Monad [\$]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17         |

|   | 2.5   | Related Work in Translation Validation and Verified Compilation*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18         |